# Western digital

C O R P O R A T / O N

# FD179X-02

# Floppy Disk Formatter/Controller Family

#### **FEATURES**

- TWO VFO CONTROL SIGNALS RG & VFOE

- SOFT SECTOR FORMAT COMPATIBILITY

- AUTOMATIC TRACK SEEK WITH VERIFICATION

- ACCOMMODATES SINGLE AND DOUBLE DENSITY FORMATS

IBM 3740 Single Density (FM)

IBM System 34 Double Density (MFM)

Non IBM Format for Increased Capacity

- READ MODE

- Single/Multiple Sector Read with Automatic Search or Entire Track Read

- Selectable 128, 256, 512 or 1024 Byte Sector Lengths

- WRITE MODE

- Single/Multiple Sector Write with Automatic Sector Search

- Entire Track Write for Diskette Formatting

- SYSTEM COMPATIBILITY

- Double Buffering of Data 8 Bit Bi-Directional Bus for Data, Control and Status

- DMA or Programmed Data Transfers

- All Inputs and Outputs are TTL Compatible

- On-Chip Track and Sector Registers/Comprehensive Status Information

- PROGRAMMABLE CONTROLS

Selectable Track to Track Stepping Time

Side Select Compare

- INTERFACES TO WD1691 DATA SEPARATOR

- WINDOW EXTENSION

- INCORPORATES ENCODING/DECODING AND ADDRESS MARK CIRCUITRY

- FD1792/4 IS SINGLE DENSITY ONLY

- FD1795/7 HAS A SIDE SELECT OUTPUT

# 179X-02 FAMILY CHARACTERISTICS

| FEATURES              | 1791 | 1792 | 1793 | 1794 | 1795 | 1797 |

|-----------------------|------|------|------|------|------|------|

| Single Density (FM)   | Х    | Х    | Х    | Χ    | Χ    | Х    |

| Double Density (MFM)  | Х    |      | Х    |      | Х    | Х    |

| True Data Bus         |      |      | X    | Х    |      | Х    |

| Inverted Data Bus     | Х    | X.   |      |      | Χ    |      |

| Write Precomp         | Х    | Х    | Χ    | Χ    | Х    | X    |

| Side Selection Output |      | 1    |      |      | Х    | Х    |

#### **APPLICATIONS**

8" FLOPPY AND 51/4" MINI FLOPPY CONTROLLER SINGLE OR DOUBLE DENSITY CONTROLLER/FORMATTER

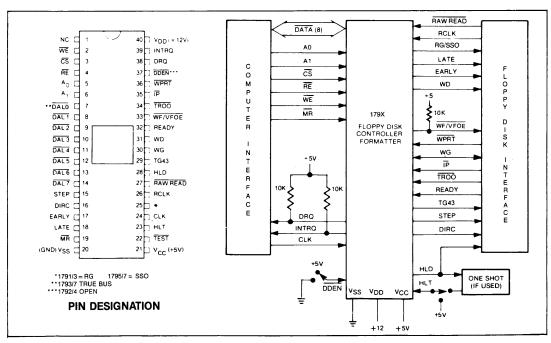

FD179X SYSTEM BLOCK DIAGRAM

# PIN OUTS

| PIN<br>NUMBER | PIN NAME              | SYMBOL          | FUNCTION                                                                                                                                                                                                                                                                                                                                          |

|---------------|-----------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | NO CONNECTION         | NC              | Pin 1 is internally connected to a back bias generator and must be left open by the user.                                                                                                                                                                                                                                                         |

| 19            | MASTER RESET          | MR              | A logic low (50 microseconds min.) on this input resets the device and loads HEX 03 into the command register. The Not Ready (Status Bit 7) is reset during MR ACTIVE. When MR is brought to a logic high a RESTORE Command is executed, regardless of the state of the Ready signal from the drive. Also, HEX 01 is loaded into sector register. |

| 20            | POWER SUPPLIES        | Vss             | Ground                                                                                                                                                                                                                                                                                                                                            |

| 21            |                       | Vcc             | +5V ±5%                                                                                                                                                                                                                                                                                                                                           |

| 40            |                       | V <sub>DD</sub> | + 12V ±5%                                                                                                                                                                                                                                                                                                                                         |

| COMPUTE       | !<br>:R INTERFACE:    |                 |                                                                                                                                                                                                                                                                                                                                                   |

| 2             | WRITE ENABLE          | WE              | A logic low on this input gates data on the DAL into the selected register when $\overline{\text{CS}}$ is low.                                                                                                                                                                                                                                    |

| 3             | CHIP SELECT           | ĊŚ              | A logic low on this input selects the chip and enables computer communication with the device.                                                                                                                                                                                                                                                    |

| 4             | READ ENABLE           | RE              | A logic low on this input controls the placement of data from a selected register on the DAL when $\overline{\text{CS}}$ is low.                                                                                                                                                                                                                  |

| 5,6           | REGISTER SELECT LINES | A0, A1          | These inputs select the register to receive/transfer data on the DAL lines under RE and WE control:                                                                                                                                                                                                                                               |

|               |                       |                 | CS A1 A0 RE WE                                                                                                                                                                                                                                                                                                                                    |

|               |                       |                 | 0         0         Status Reg         Command Reg           0         0         1         Track Reg         Track Reg           0         1         0         Sector Reg         Sector Reg           0         1         1         Data Reg         Data Reg                                                                                    |

| 7-14          | DATA ACCESS LINES     | DALO-DAL7       | Eight bit Bidirectional bus used for transfer of data, control, and status. This bus is receiver enabled by WE or transmitter enabled by RE. Each line will drive 1 standard TTL load.                                                                                                                                                            |

| 24            | CLOCK                 | CLK             | This input requires a free-running 50% duty cycle square wave clock for internal timing reference, 2 MHz ± 1% for 8" drives, 1 MHz ± 1% for mini-floppies.                                                                                                                                                                                        |

| 38            | DATA REQUEST          | DRQ             | This open drain output indicates that the DR contains assembled data in Read operations, or the DR is empty in Write operations. This signal is reset when serviced by the computer through reading or loading the DR in Read or Write operations, respectively. Use 10K pull-up resistor to +5.                                                  |

| 39            | INTERRUPT REQUEST     | INTRQ           | This open drain output is set at the completion of any command and is reset when the STATUS register is read or the command register is written to. Use 10K pull-up resistor to +5.                                                                                                                                                               |

| FLOPPY D      | ISK INTERFACE:        |                 |                                                                                                                                                                                                                                                                                                                                                   |

| 15            | STEP                  | STEP            | The step output contains a pulse for each step.                                                                                                                                                                                                                                                                                                   |

| 16            | DIRECTION             | DIRC            | Direction Output is active high when stepping in, active low when stepping out.                                                                                                                                                                                                                                                                   |

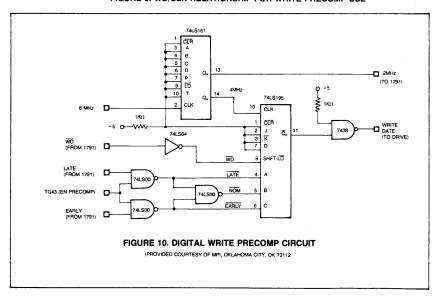

| 17            | EARLY                 | EARLY           | Indicates that the WRITE DATA pulse occuring while Early is active (high) should be shifted early for write precompensation.                                                                                                                                                                                                                      |

| 18            | LATE                  | LATE            | Indicates that the write data pulse occurring while Late is active (high) should be shifted late for write precompensation.                                                                                                                                                                                                                       |

| PIN<br>NUMBER | PIN NAME                              | SYMBOL   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|---------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22            | TEST                                  | TEST     | This input is used for testing purposes only and should be tied to +5V or left open by the user unless interfacing to voice coil actuated steppers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

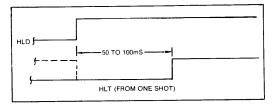

| 23            | HEAD LOAD TIMING                      | HLT      | When a logic high is found on the HLT input the head is assumed to be engaged. It is typically derived from a 1 shot triggered by HLD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

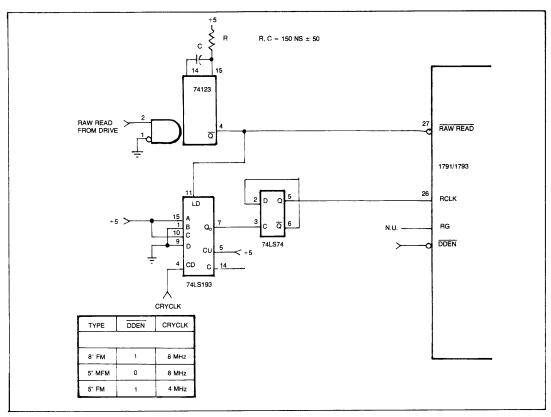

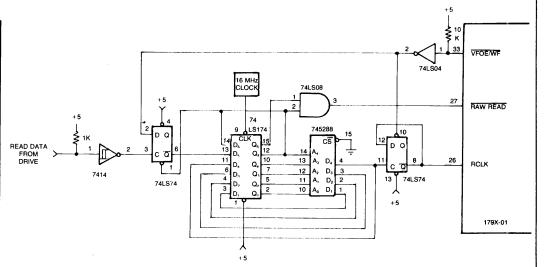

| 25            | READ GATE<br>(1791, 1792, 1793, 1794) | RG       | This output is used for synchronization of external data separators. The output goes high after two Bytes of zeros in single density, or 4 Bytes of either zeros or ones in double density operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 25            | SIDE SELECT OUTPUT<br>(1795, 1797)    | SSO      | The logic level of the Side Select Output is directly controlled by the 'S' flag in Type II or III commands. When U = 1, SSO is set to a logic 1. When U = 0, SSO is set to a logic 0. The SSO is compared with the side information in the Sector I.D. Field. If they do not compare Status Bit 4 (RNF) is set. The Side Select Output is only updated at the beginning of a Type II or III command. It is forced to a logic 0 upon a MASTER RESET condition.                                                                                                                                                                                                                                                                                                                |

| 26            | READ CLOCK                            | RCLK     | A nominal square-wave clock signal derived from the data stream must be provided to this input. Phasing (i.e. RCLK transitions) relative to RAW READ is important but polarity (RCLK high or low) is not.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27            | RAW READ                              | RAW READ | The data input signal directly from the drive. This input shall be a negative pulse for each recorded flux transition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28            | HEAD LOAD                             | HLD      | The HLD output controls the loading of the Read-Write head against the media.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 29            | TRACK GREATER THAN 43                 | TG43     | This output informs the drive that the Read/Write head is positioned between tracks 44-76. This output is valid only during Read and Write Commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

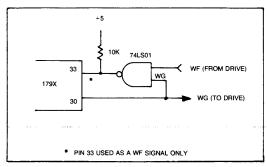

| 30            | WRITE GATE                            | WG       | This output is made valid before writing is to be performed on the diskette.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

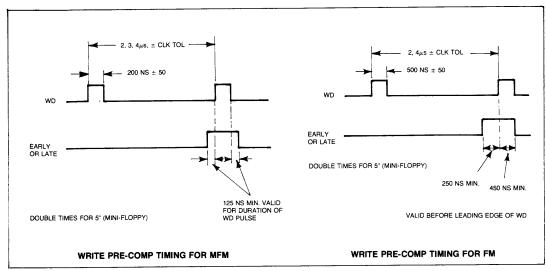

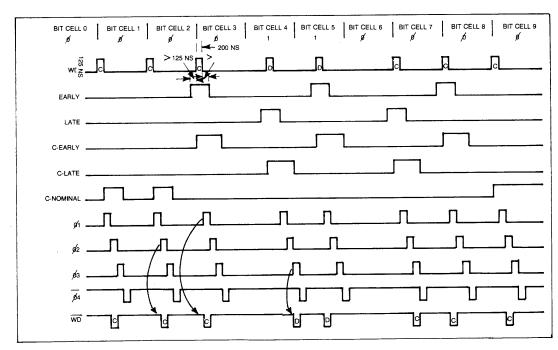

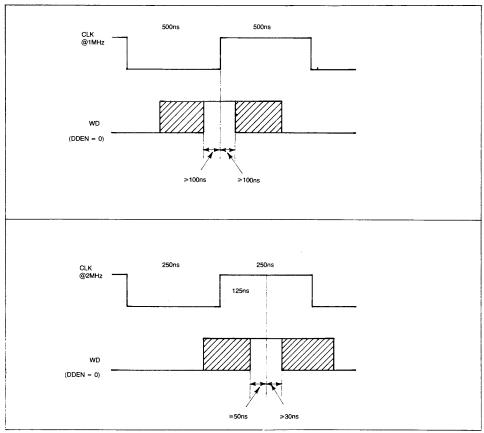

| 31            | WRITE DATA                            | WD       | A 200 ns (MFM) or 500 ns (FM) output pulse per flux transition. WD contains the unique Address marks as well as data and clock in both FM and MFM formats.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 32            | READY                                 | READY    | This input indicates disk readiness and is sampled for a logic high before Read or Write commands are performed. If Ready is low the Read or Write operation is not performed and an interrupt is generated. Type I operations are performed regardless of the state of Ready. The Ready input appears in inverted format as Status Register bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                           |

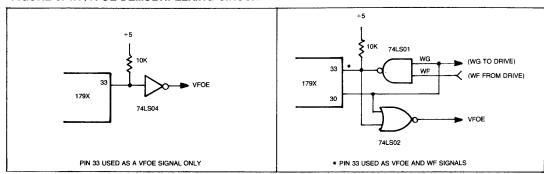

| 33            | WRITE FAULT<br>VFO ENABLE             | WF/VFOE  | This is a bi-directional signal used to signify writing faults at the drive, and to enable the external PLO data separator. When WG = 1, Pin 33 functions as a WF input. If WF = 0, any write command will immediately be terminated. When WG = 0, Pin 33 functions as a VFOE output. VFOE will go low during a read operation after the head has loaded and settled (HLT = 1). On the 1795/7, it will remain low until the last bit of the second CRC byte in the ID field. VFOE will then go high until 8 bytes (MFM) or 4 bytes (FM) before the Address Mark. It will then go active until the last bit of the second CRC byte of the Data Field. On the 1791/3, VFOE will remain low until the end of the Data Field. This pin has an internal 100K Ohm pull-up resistor. |

| 34            | TRACK 00                              | TR00     | This input informs the FD179X that the Read/Write head is positioned over Track 00.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIN NUMBER | PIN NAME       | SYMBOL | FUNCTION                                                                                                                                                                                                                       |

|------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35         | INDEX PULSE    | ĪΡ     | This input informs the FD179X when the index hole is encountered on the diskette.                                                                                                                                              |

| 36         | WRITE PROTECT  | WPRT   | This input is sampled whenever a Write Command is received. A logic low terminates the command and sets the Write Protect Status bit.                                                                                          |

| 37         | DOUBLE DENSITY | DDEN   | This input pin selects either single or double density operation. When $\overline{DDEN} = 0$ , double density is selected. When $\overline{DDEN} = 1$ , single density is selected. This line must be left open on the 1792/4. |

# **GENERAL DESCRIPTION**

The FD179X are N-Channel Silicon Gate MOS LSI devices which perform the functions of a Floppy Disk Formatter/Controller in a single chip implementation. The FD179X, which can be considered the end result of both the FD1771 and FD1781 designs, is IBM 3740 compatible in single density mode (FM) and System 34 compatible in Double Density Mode (MFM). The FD179X contains all the features of its predecessor the FD1771, plus the added features necessary to read/write and format a double density diskette. These include address mark detection, FM and MFM encode and decode logic, window extension, and write precompensation. In order to maintain compatibility, the FD1771, FD1781, and FD179X designs were made as close as possible with the computer interface, instruction set, and I/O registers being identical. Also, head load control is identical. In each case, the actual pin assignments vary by only a few pins from any one to another.

The processor interface consists of an 8-bit bi-directional bus for data, status, and control word transfers. The FD179X is set up to operate on a multiplexed bus with other bus-oriented devices.

The FD179X is TTL compatible on all inputs and outputs. The outputs will drive ONE TTL load or three LS loads. The 1793 is identical to the 1791 except the DAL lines are TRUE for systems that utilize true data busses.

The 1795/7 has a side select output for controlling double sided drives, and the 1792 and 1794 are "Single Density Only" versions of the 1791 and 1793 respectively. On these devices, DDEN must be left open.

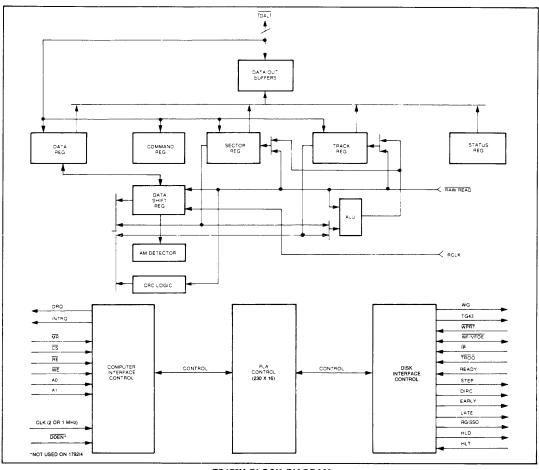

### ORGANIZATION

The Floppy Disk Formatter block diagram is illustrated on page 5. The primary sections include the parallel processor interface and the Floppy Disk interface.

Data Shift Register — This 8-bit register assembles serial data from the Read Data input (RAW READ) during Read operations and transfers serial data to the Write Data output during Write operations.

Data Register — This 8-bit register is used as a holding register during Disk Read and Write operations. In Disk Read operations the assembled data byte is transferred in parallel to the Data Register from the Data Shift Register. In Disk Write operations information is transferred in parallel from the Data Register to the Data Shift Register.

When executing the Seek command the Data Register holds the address of the desired Track position. This register is loaded from the DAL and gated onto the DAL under processor control.

Track Register — This 8-bit register holds the track number of the current Read/Write head position. It is incremented by one every time the head is stepped in (towards track 76) and decremented by one when the head is stepped out (towards track 00). The contents of the register are compared with the recorded track number in the ID field during disk Read, Write, and Verify operations. The Track Register can be loaded from or transferred to the DAL. This Register should not be loaded when the device is busy.

Sector Register (SR) — This 8-bit register holds the address of the desired sector position. The contents of the register are compared with the recorded sector number in the ID field during disk Read or Write operations. The Sector Register contents can be loaded from or transferred to the DAL. This register should not be loaded when the device is busy.

Command Register (CR) — This 8-bit register holds the command presently being executed. This register should not be loaded when the device is busy unless the new command is a force interrupt. The command register can be loaded from the DAL, but not read onto the DAL.

Status Register (STR) — This 8-bit register holds device Status information. The meaning of the Status bits is a function of the type of command previously executed. This register can be read onto the DAL, but not loaded from the DAL.

**CRC Logic** — This logic is used to check or to generate the 16-bit Cyclic Redundancy Check (CRC). The polynomial is:  $G(x) = x^{16} + x^{12} + x^5 + 1$ .

The CRC includes all information starting with the address mark and up to the CRC characters. The CRC register is preset to ones prior to data being shifted through the circuit.

**Arithmetic/Logic Unit (ALU)** — The ALU is a serial comparator, incrementer, and decrementer and is used for register modification and comparisons with the disk recorded ID field.

**Timing and Control** — All computer and Floppy Disk Interface controls are generated through this logic. The internal device timing is generated from an external crystal clock.

The FD179X has two different modes of operation according to the state of  $\overline{\text{DDEN}}$ . When  $\overline{\text{DDEN}}=0$  double density (MFM) is assumed. When  $\overline{\text{DDEN}}=1$ , single

FD179X BLOCK DIAGRAM

density (FM) is assumed. 1792 & 1794 are single density only.

**AM Detector** — The address mark detector detects ID, data and index address marks during read and write operations.

## PROCESSOR INTERFACE

The interface to the processor is accomplished through the eight Data Access Lines (DAL) and associated control signals. The DAL are used to transfer Data, Status, and Control words out of, or into the FD179X. The DAL are three state buffers that are enabled as output drivers when Chip Select (CS) and Read Enable (RE) are active (low logic state) or act as input receivers when CS and Write Enable (WE) are active.

When transfer of data with the Floppy Disk Controller is required by the host processor, the device address is decoded and  $\overline{\text{CS}}$  is made low. The address bits A1 and A0, combined with the signals  $\overline{\text{RE}}$  during a Read operation or  $\overline{\text{WE}}$  during a Write operation are interpreted as selecting the following registers:

| A1 | - A0 | READ (RE)       | WRITE (WE)       |

|----|------|-----------------|------------------|

| 0  | 0    | Status Register | Command Register |

| 0  | 1    | Track Register  | Track Register   |

| 1  | 0    | Sector Register | Sector Register  |

| 1  | 1    | Data Register   | Data Register    |

During Direct Memory Access (DMA) types of data transfers between the Data Register of the FD179X and the processor, the Data Request (DRQ) output is used in Data Transfer control. This signal also appears as status bit 1 during Read and Write operations.

On Disk Read operations the Data Request is activated (set high) when an assembled serial input byte is transferred in parallel to the Data Register. This bit is cleared when the Data Register is read by the processor. If the Data Register is read after one or more characters are lost, by having new data transferred into the register prior to processor readout, the Lost Data bit is set in the Status Register. The Read operation continues until the end of sector is reached.

On Disk Write operations the data Request is activated when the Data Register transfers its contents to the Data

Shift Register, and requires a new data byte. It is reset when the Data Register is loaded with new data by the processor. If new data is not loaded at the time the next serial byte is required by the Floppy Disk, a byte of zeroes is written on the diskette and the Lost Data bit is set in the Status Register.

At the completion of every command an INTRQ is generated. INTRQ is reset by either reading the status register or by loading the command register with a new command. In addition, INTRQ is generated if a Force Interrupt command condition is met.

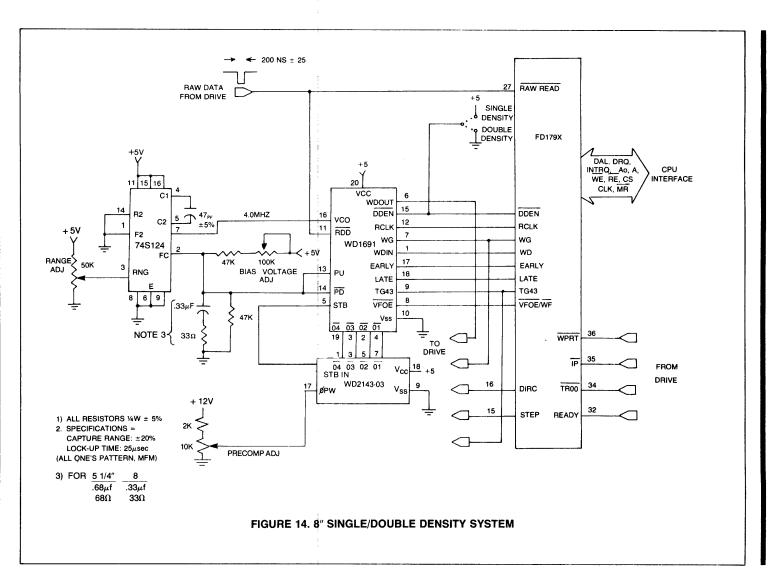

The 179X has two modes of operation according to the state of DDEN (Pin 37). When DDEN = 1, single density is selected. In either case, the CLK input (Pin 24) is at 2 MHz. However, when interfacing with the mini-floppy, the CLK input is set at 1 MHz for both single density and double density.

# **GENERAL DISK READ OPERATIONS**

Sector lengths of 128, 256, 512 or 1024 are obtainable in either FM or MFM formats. For FM, DDEN should be placed to logical "1." For MFM formats, DDEN should be placed to a logical "0." Sector lengths are determined at format time by the fourth byte in the "ID" field.

| Sector L      | Sector Length Table* |  |  |  |  |  |  |  |

|---------------|----------------------|--|--|--|--|--|--|--|

| Sector Length | Number of Bytes      |  |  |  |  |  |  |  |

| Field (hex)   | in Sector (decimal)  |  |  |  |  |  |  |  |

| 00            | 128                  |  |  |  |  |  |  |  |

| 01            | 256                  |  |  |  |  |  |  |  |

| 02            | 512                  |  |  |  |  |  |  |  |

| 03            | 1024                 |  |  |  |  |  |  |  |

\*1795/97 may vary — see command summary.

The number of sectors per track as far as the FD179X is concerned can be from 1 to 255 sectors. The number of tracks as far as the FD179X is concerned is from 0 to 255 tracks. For IBM 3740 compatibility, sector lengths are 128 bytes with 26 sectors per track. For System 34 compatibility (MFM), sector lengths are 256 bytes/sector with 26 sectors/track; or lengths of 1024 bytes/sector with 8 sectors/track. (See Sector Length Table)

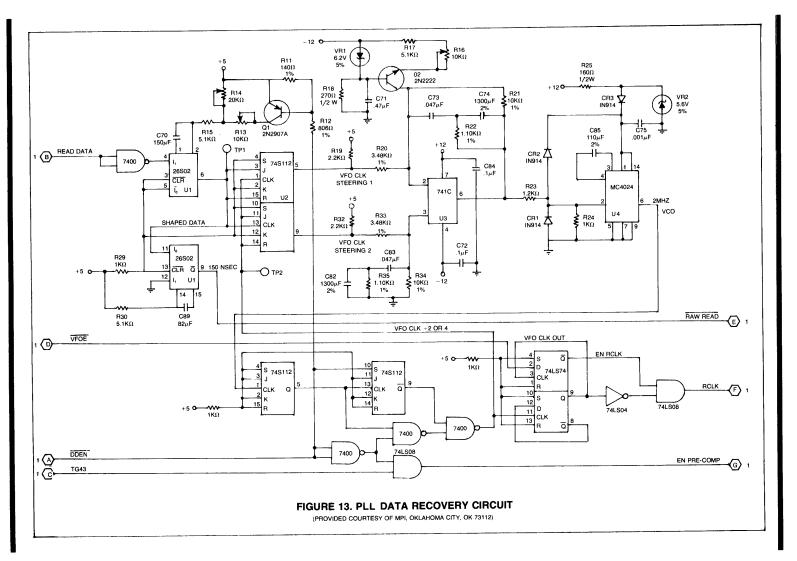

For read operations in 8" double density the FD179X requires RAW READ Data (Pin 27) signal which is a 200 ns pulse per flux transition and a Read clock (RCLK) signal to indicate flux transition spacings. The RCLK (Pin 26) signal is provided by some drives but if not it may be derived externally by Phase lock loops, one shots, or counter techniques. In addition, a Read Gate Signal is provided as an output (Pin 25) on 1791/92/93/94 which can be used to inform phase lock loops when to acquire synchronization. When reading from the media in FM. RG is made true when 2 bytes of zeroes are detected. The FD179X must find an address mark within the next 10 bytes; otherwise RG is reset and the search for 2 bytes of zeroes begins all over again. If an address mark is found within 10 bytes, RG remains true as long as the FD179X is deriving any useful information from the data stream. Similarly for MFM, RG is made active when 4 bytes of "00" or "FF" are detected. The FD179X must find an address mark within the next 16 bytes, otherwise RG is reset and search resumes.

During read operations (WG = 0), the  $\overline{\text{VFOE}}$  (Pin 33) is provided for phase lock loop synchronization.  $\overline{\text{VFOE}}$  will go active low when:

- a) Both HLT and HLD are True

- b) Settling Time, if programmed, has expired

- c) The 179X is inspecting data off the disk

If WF/VFOE is not used, leave open or tie to a 10K resistor to +5.

#### **GENERAL DISK WRITE OPERATION**

When writing is to take place on the diskette the Write Gate (WG) output is activated, allowing current to flow into the Read/Write head. As a precaution to erroneous writing the first data byte must be loaded into the Data Register in response to a Data Request from the FD179X before the Write Gate signal can be activated.

Writing is inhibited when the Write Protect input is a logic low, in which case any Write command is immediately terminated, an interrupt is generated and the Write Protect status bit is set. The Write Fault input, when activated, signifies a writing fault condition detected in disk drive electronics such as failure to detect write current flow when the Write Gate is activated. On detection of this fault the FD179X terminates the current command, and sets the Write Fault bit (bit 5) in the Status Word. The Write Fault input should be made inactive when the Write Gate output becomes inactive.

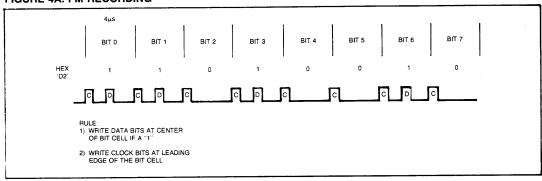

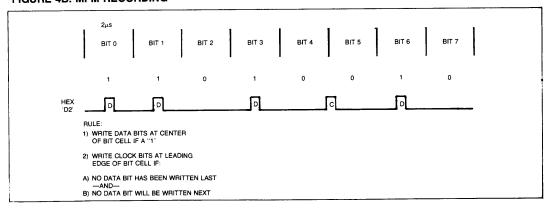

For write operations, the FD179X provides Write Gate (Pin 30) and Write Data (Pin 31) outputs. Write data consists of a series of 500 ns pulses in FM (DDEN = 1) and 200 ns pulses in MFM (DDEN = 0). Write Data provides the unique address marks in both formats.

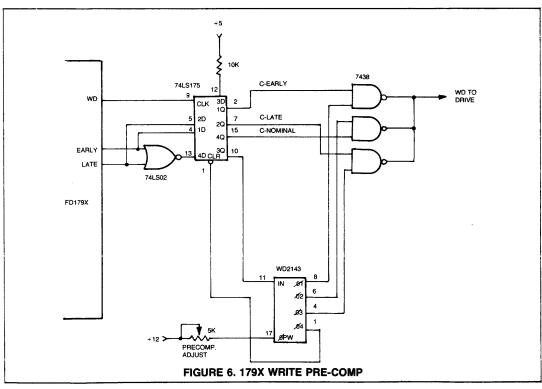

Also during write, two additional signals are provided for write precompensation. These are EARLY (Pin 17) and LATE (Pin 18). EARLY is active true when the WD pulse appearing on (Pin 30) is to be written EARLY. LATE is active true when the WD pulse is to be written LATE. If both EARLY and LATE are low when the WD pulse is present, the WD pulse is to be written at nominal. Since write precompensation values vary from disk manufacturer to disk manufacturer, the actual value is determined by several one shots or delay lines which are located external to the FD179X. The write precompensation signals EARLY and LATE are valid for the duration of WD in both FM and MFM formats.

#### READY

Whenever a Read or Write command (Type II or III) is received the FD179X samples the Ready input. If this input is logic low the command is not executed and an interrupt is generated. All Type I commands are performed regardless of the state of the Ready input. Also, whenever a Type II or III command is received, the TG43 signal output is updated.

### COMMAND DESCRIPTION

The FD179X will accept eleven commands. Command words should only be loaded in the Command Register when the Busy status bit is off (Status bit 0). The one exception is the Force Interrupt command. Whenever a command is being executed, the Busy status bit is set. When a command is completed, an interrupt is generated and the Busy status bit is reset. The Status Register indicates whether the completed command encountered an error or was fault free. For ease of discussion, commands are divided into four types. Commands and types are summarized in Table 1.

# TABLE 1. COMMAND SUMMARY.

A. Commands for Models: 1791, 1792, 1793, 1794

B. Commands for Models: 1795, 1797

|      |                 |   |   |   | В | its |    |                |                |   |   |   | В | its |    |                |                |

|------|-----------------|---|---|---|---|-----|----|----------------|----------------|---|---|---|---|-----|----|----------------|----------------|

| Type | Command         | 7 | 6 | 5 | 4 | 3   | 2  | 1              | 0              | 7 | 6 | 5 | 4 | 3   | 2  | 1              | 0              |

|      | Restore         | 0 | 0 | 0 | 0 | h   | ٧  | r <sub>1</sub> | r <sub>0</sub> | 0 | 0 | 0 | 0 | h   | V  | r <sub>1</sub> | ro             |

| 1    | Seek            | 0 | 0 | 0 | 1 | h   | ٧  | r <sub>1</sub> | ro             | 0 | 0 | 0 | 1 | h   | v  | ri             | ro             |

| - 1  | Step            | 0 | 0 | 1 | T | h   | ٧  | r <sub>1</sub> | ro             | 0 | 0 | 1 | Т | h   | ٧  | r <sub>1</sub> | ro             |

| ı    | Step-in         | 0 | 1 | 0 | Т | h   | ٧  | r <sub>1</sub> | ro             | 0 | 1 | 0 | Т | h   | ٧  | r <sub>1</sub> | ro             |

| - 1  | Step-out        | 0 | 1 | 1 | T | h   | ٧  | r <sub>1</sub> | ro             | 0 | 1 | 1 | T | h   | ٧  | r <sub>1</sub> | ro             |

| II   | Read Sector     | 1 | 0 | 0 | m | s   | Ε  | С              | 0              | 1 | 0 | 0 | m | L   | E  | U              | o l            |

| 11   | Write Sector    | 1 | 0 | 1 | m | S   | Ε  | С              | a <sub>0</sub> | 1 | 0 | 1 | m | L   | Ε  | U              | a <sub>0</sub> |

| 111  | Read Address    | 1 | 1 | 0 | 0 | 0   | Ε  | 0              | 0              | 1 | 1 | 0 | 0 | 0   | Ε  | U              | 0              |

| 111  | Read Track      | 1 | 1 | 1 | 0 | 0   | Ε  | 0              | 0              | 1 | 1 | 1 | 0 | 0   | Ε  | U              | 0              |

| III  | Write Track     | 1 | 1 | 1 | 1 | 0   | Ε  | 0              | 0              | 1 | 1 | 1 | 1 | 0   | Ε  | U              | 0              |

| IV   | Force Interrupt | 1 | 1 | 0 | 1 | lз  | 12 | 11             | l0             | 1 | 1 | 0 | 1 | lз  | 12 | 11             | lo l           |

# FLAG SUMMARY

# **TABLE 2. FLAG SUMMARY**

| Command<br>Type | Bit<br>No(s) |                                                             | Description                                                                                 |  |  |  |  |

|-----------------|--------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| I               | 0, 1         | r1 r0 = Stepping Motor Rate<br>See Table 3 for Rate Summary | ·                                                                                           |  |  |  |  |

| ı               | 2            | V = Track Number Verify Flag                                | V = 0, No verify<br>V = 1, Verify on destination track                                      |  |  |  |  |

| I               | 3            | h = Head Load Flag                                          | h = 1, Load head at beginning h = 0, Unload head at beginning                               |  |  |  |  |

| 1               | 4            | T = Track Update Flag                                       | T = 0, No update<br>T = 1, Update track register                                            |  |  |  |  |

| Н               | 0            | a <sub>0</sub> = Data Address Mark                          | a <sub>0</sub> = 0, FB (DAM)<br>a <sub>0</sub> = 1, F8 (deleted DAM)                        |  |  |  |  |

| П               | 1            | C = Side Compare Flag                                       | C = 0, Disable side compare<br>C = 1, Enable side compare                                   |  |  |  |  |

| 11 & 111        | 1            | U = Update SSO                                              | U = 0, Update SSO to 0<br>U = 1, Update SSO to 1                                            |  |  |  |  |

| 11 & 111        | 2            | E = 15 MS Delay                                             | E = 0, No 15 MS delay<br>E = 1, 15 MS delay                                                 |  |  |  |  |

| II              | 3            | S = Side Compare Flag                                       | S = 0, Compare for side 0<br>S = 1, Compare for side 1                                      |  |  |  |  |

| 11              | 3            | L = Sector Length Flag                                      | LSB's Sector Length in ID Field 00 01 10 11  L = 0 256 512 1024 128  L = 1 128 256 512 1024 |  |  |  |  |

| 11              | 4            | m = Multiple Record Flag                                    | m = 0, Single record<br>m = 1, Multiple records                                             |  |  |  |  |

| IV              | 0-3          | Ix                                                          |                                                                                             |  |  |  |  |

<sup>\*</sup>NOTE: See Type IV Command Description for further information.

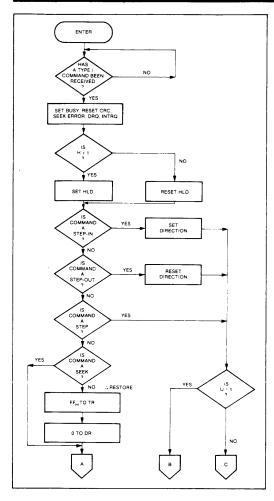

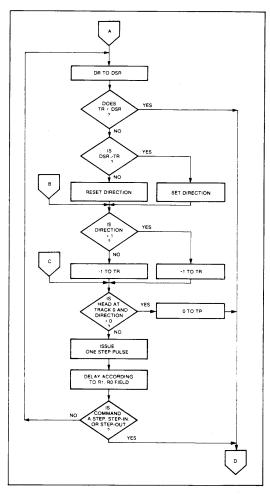

# TYPE I COMMANDS

The Type I Commands include the Restore, Seek, Step, Step-In, and Step-Out commands. Each of the Type I Commands contains a rate field (f0 f1), which determines the stepping motor rate as defined in Table 3.

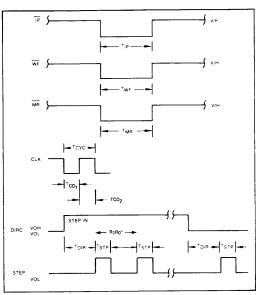

A 2  $\mu s$  (MFM) or 4  $\mu s$  (FM) pulse is provided as an output to the drive. For every step pulse issued, the drive moves one track location in a direction determined by the direction output. The chip will step the drive in the same direction it last stepped unless the command changes the direction.

The Direction signal is active high when stepping in and low when stepping out. The Direction signal is valid 12  $\mu$ s before the first stepping pulse is generated.

The rates (shown in Table 3) can be applied to a Step-Direction Motor through the device interface.

TABLE 3. STEPPING RATES

|   | CL  | .ĸ | 2 MHz  | 2 MHz  | 1 MHz  | 1 MHz  | 2 MHz  | 1 MHz  |

|---|-----|----|--------|--------|--------|--------|--------|--------|

| 1 | DD  | EN | 0      | 1      | 0      | 1      | ×      | ×      |

|   | R1  | RO | TEST=1 | TEST=1 | TEST=1 | TEST=1 | TEST=0 | TEST=0 |

| ٠ | 0   | 0  | 3 ms   | 3 ms   | 6 ms   | 6 ms   | 184μs  | 368µs  |

|   | 0   | 1  | 6 ms   | 6 ms   | 12 ms  | 12 ms  | 190μs  | 380μs  |

|   | - 1 | 0  | 10 ms  | 10 ms- | 20 ms  | 20 ms  | 198µs  | 396μs  |

|   | 1   | 1  | 15 ms  | 15 ms  | 30 ms  | 30 ms  | 208μs  | 416μs  |

|   | 1   |    |        |        |        |        |        |        |

After the last directional step an additional 15 milliseconds of head settling time takes place if the Verify flag is set in Type I commands. Note that this time doubles to 30 ms for a 1 MHz clock. If  $\overline{\text{TEST}} = 0$ , there is zero settling time. There is also a 15 ms head settling time if the E flag is set in any Type II or III command.

When a Seek, Step or Restore command is executed an optional verification of Read-Write head position can be performed by settling bit  $2\,(V=1)$  in the command word to a logic 1. The verification operation begins at the end of the 5 millisecond settling time after the head is loaded against the media. The track number from the first encountered ID Field is compared against the contents of the Track Register. If the track numbers compare and the ID Field Cyclic Redundancy Check (CRC) is correct, the verify operation is complete and an INTRQ is generated with no errors. If there is a match but not a valid CRC, the CRC error status bit is set (Status bit 3), and the next encountered ID field is read from the disk for the verification operation.

The FD179X must find an ID field with correct track number and correct CRC within 5 revolutions of the media; otherwise the seek error is set and an INTRQ is generated. If V=0, no verification is performed.

The Head Load (HLD) output controls the movement of the read/write head against the media. HLD is activated at the beginning of a Type I command if the h flag is set (h = 1), at the end of the Type I command if the verify flag (V = 1), or upon receipt of any Type II or III command. Once HLD is active it remains active until either a Type I command is received with (h = 0 and V = 0); or if the FD179X is in an idle state (non-busy) and 15 index pulses have occurred.

Head Load timing (HLT) is an input to the FD179X which is used for the head engage time. When HLT = 1, the FD179X assumes the head is completely engaged. The head engage time is typically 30 to 100 ms depending on drive. The low to high transition on HLD is typically used to fire a one shot. The output of the one shot is then used for HLT and supplied as an input to the FD179X.

#### **HEAD LOAD TIMING**

When both HLD and HLT are true, the FD179X will then read from or write to the media. The "and" of HLD and HLT appears as status Bit 5 in Type I status.

In summary for the Type I commands: if h=0 and V=0, HLD is reset. If h=1 and V=0, HLD is set at the beginning of the command and HLT is not sampled nor is there an internal 15 ms delay. If h=0 and V=1, HLD is set near the end of the command, an internal 15 ms occurs, and the FD179X waits for HLT to be true. If h=1 and h=10, HLD is set at the beginning of the command. Near the end of the command, after all the steps have been issued, an internal 15 ms delay occurs and the FD179X then waits for HLT to occur.

For Type II and III commands with E flag off, HLD is made active and HLT is sampled until true. With E flag on, HLD is made active, an internal 15 ms delay occurs and then HLT is sampled until true.

#### RESTORE (SEEK TRACK 0)

Upon receipt of this command the Track 00 (TR00) input is sampled. If TR00 is active low indicating the Read-Write head is positioned over track 0, the Track Register is loaded with zeroes and an interrupt is generated. If TR00 is not active low, stepping pulses (pins 15 to 16) at a rate specified by the f1 f0 field are issued until the TR00 input is activated. At this time the Track Register is loaded with zeroes and an interrupt is generated. If the TR00 input does not go active low after 255 stepping pulses, the FD179X terminates operation, interrupts, and sets the Seek error status bit, providing the V flag is set. A verification operation also takes place if the V flag is set. The h bit allows the head to be loaded at the start of command. Note that the Restore command is executed when MR goes from an active to an inactive state and that the DRQ pin stays low.

# SEEK

This command assumes that the Track Register contains the track number of the current position of the Read-Write head and the Data Register contains the desired track number. The FD179X will update the Track register and issue stepping pulses in the appropriate direction until the contents of the Track register are equal to the contents of

the Data Register (the desired track location). A verification operation takes place if the V flag is on. The h bit allows the head to be loaded at the start of the command. An interrupt is generated at the completion of the command. Note: When using multiple drives, the track register must be updated for the drive selected before seeks are issued.

# STEP

Upon receipt of this command, the FD179X issues one stepping pulse to the disk drive. The stepping motor direction is the same as in the previous step command. After a delay determined by the f1f0 field, a verification takes place if the V flag is on. If the U flag is on, the Track Register is updated. The h bit allows the head to be loaded at the start of the command. An interrupt is generated at the completion of the command.

#### STEP-IN

Upon receipt of this command, the FD179X issues one stepping pulse in the direction towards track 76. If the U

TYPE I COMMAND FLOW

flag is on, the Track Register is incremented by one. After a delay determined by the  $^{r1}$ °0 field, a verification takes place if the V flag is on. The h bit allows the head to be loaded at the start of the command. An interrupt is generated at the completion of the command.

#### STEP-OUT

Upon receipt of this command, the FD179X issues one stepping pulse in the direction towards track 0. If the U flag is on, the Track Register is decremented by one. After a delay determined by the '11'0 field, a verification takes place if the V flag is on. The h bit allows the head to be loaded at the start of the command. An interrupt is generated at the completion of the command.

# **EXCEPTIONS**

On the 1795/7 devices, the SSO output is not affected during Type 1 commands, and an internal side compare does not take place when the (V) Verify Flag is on.

TYPE I COMMAND FLOW

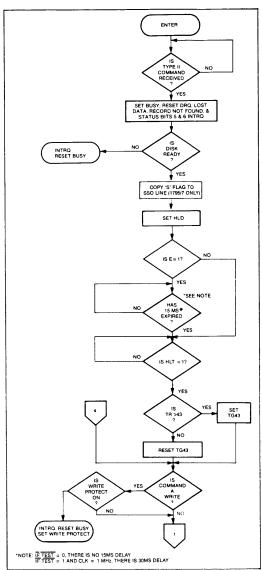

#### TYPE II COMMANDS

The Type II Commands are the Read Sector and Write Sector commands. Prior to loading the Type II Command into the Command Register, the computer must load the Sector Register with the desired sector number. Upon receipt of the Type II command, the busy status Bit is set. If the E flag = 1 (this is the normal case) HLD is made active and HLT is sampled after a 15 msec delay. If the E flag is 0, the head is loaded and HLT sampled with no 15 msec delay. The ID field and Data Field format are shown on page 13.

When an ID field is located on the disk, the FD179X compares the Track Number on the ID field with the Track Register. If there is not a match, the next encountered ID field is read and a comparison is again made. If there was a match, the Sector Number of the ID field is compared with the Sector Register. If there is not a Sector match, the next encountered ID field is read off the disk and comparisons again made. If the ID field CRC is correct, the data field is

then located and will be either written into, or read from depending upon the command. The FD179X must find an ID field with a Track number, Sector number, side number, and CRC within four revolutions of the disk; otherwise, the Record not found status bit is set (Status bit 3) and the command is terminated with an interrupt.

TYPE II COMMAND

Each of the Type II Commands contains an (m) flag which determines if multiple records (sectors) are to be read or written, depending upon the command. If m=0, a single sector is read or written and an interrupt is generated at the completion of the command. If m=1, multiple records are read or written with the sector register internally updated so that an address verification can occur on the next

record. The FD179X will continue to read or write multiple records and update the sector register in numerical ascending sequence until the sector register exceeds the number of sectors on the track or until the Force Interrupt command is loaded into the Command Register, which terminates the command and generates an interrupt.

For example: If the FD179X is instructed to read sector 27 and there are only 26 on the track, the sector register exceeds the number available. The FD179X will search for 5 disk revolutions, interrupt out, reset busy, and set the record not found status bit.

The Type II commands for 1791-94 also contain side select compare flags. When C=0 (Bit 1) no side comparison is made. When C=1, the LSB of the side number is read off the ID Field of the disk and compared with the contents of the (S) flag (Bit 3). If the S flag compares with the side number recorded in the ID field, the FD179X continues with the ID search. If a comparison is not made within 5 index pulses, the interrupt line is made active and the Record-Not-Found status bit is set

INTRO, RESET BUSY SET RECORD-NOT FOUND NO DETECTED YES YES DOES YES DOES - SIDE NO OF ID FIELD YES RING IN SECTOR LENGTH FIELD STORE LENGTH IN INTERNAL REGISTER RESET COMMAND A WRITE READ YES

TYPE II COMMAND

The Type II and III commands for the 1795-97 contain a side select flag (Bit 1). When U=0, SSO is updated to 0. Similarly, U=1 updates SSO to 1. The chip compares the SSO to the ID field. If they do not compare within 5 revolutions the interrupt line is made active and the RNF status bit is set

The 1795/7 READ SECTOR and WRITE SECTOR commands include a 'L' flag. The 'L' flag, in conjunction with the sector length byte of the ID Field, allows different byte lengths to be implemented in each sector. For IBM compatability, the 'L' flag should be set to a one.

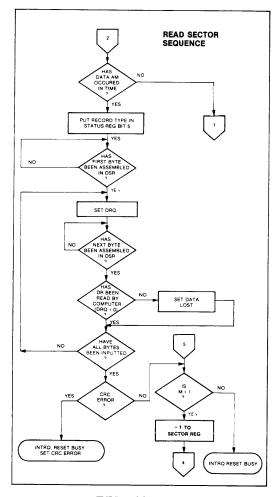

#### READ SECTOR

Upon receipt of the Read Sector command, the head is loaded, the Busy status bit set, and when an ID field is encountered that has the correct track number, correct sector number, correct side number, and correct CRC, the data field is presented to the computer. The Data Address

TYPE II COMMAND

TYPE II COMMAND

Mark of the data field must be found within 30 bytes in single density and 43 bytes in double density of the last ID field CRC byte; if not, the ID field is searched for and verified again followed by the Data Address Mark search. If after 5 revolutions the DAM cannot be found, the Record Not Found status bit is set and the operation is terminated. When the first character or byte of the data field has been shifted through the DSR, it is transferred to the DR, and DRQ is generated. When the next byte is accumulated in the DSR, it is transferred to the DR and another DRQ is generated. If the Computer has not read the previous contents of the DR before a new character is transferred that character is lost and the Lost Data Status bit is set. This sequence continues until the complete data field has been inputted to the computer. If there is a CRC error at the end of the data field, the CRC error status bit is set, and the command is terminated (even if it is a multiple record

At the end of the Read operation, the type of Data Address Mark encountered in the data field is recorded in the Status Register (Bit 5) as shown:

| STATUS |  |

|--------|--|

| RIT 5  |  |

Deleted Data Mark

Data Mark

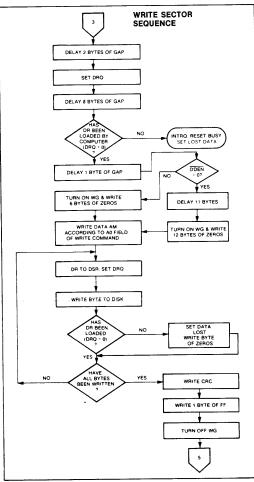

#### WRITE SECTOR

Upon receipt of the Write Sector command, the head is loaded (HLD active) and the Busy status bit is set. When an ID field is encountered that has the correct track number, correct sector number, correct side number, and correct CRC, a DRQ is generated. The FD179X counts off 11 bytes in single density and 22 bytes in double density from the CRC field and the Write Gate (WG) output is made active if the DRQ is serviced (i.e., the DR has been loaded by the computer). If DRQ has not been serviced, the command is terminated and the Lost Data status bit is set. If the DRQ has been serviced, the WG is made active and six bytes of zeroes in single density and 12 bytes in double density are then written on the disk. At this time the Data Address Mark is then written on the disk as determined by the a0 field of the command as shown below:

| a0 | Data Address Mark (Bit 0) |  |

|----|---------------------------|--|

| 1  | Deleted Data Mark         |  |

| 0  | Data Mark                 |  |

The FD179X then writes the data field and generates DRQ's to the computer. If the DRQ is not serviced in time for continuous writing the Lost Data Status Bit is set and a byte of zeroes is written on the disk. The command is not terminated. After the last data byte has been written on the disk, the two-byte CRC is computed internally and written on the disk followed by one byte of logic ones in FM or in MFM. The WG output is then deactivated. For a 2 MHz clock the INTRQ will set 8 to 12  $\mu$ sec after the last CRC byte is written. For partial sector writing, the proper method is to write the data and fill the balance with zeroes. By letting the chip fill the zeroes, errors may be masked by the lost data status and improper CRC Bytes.

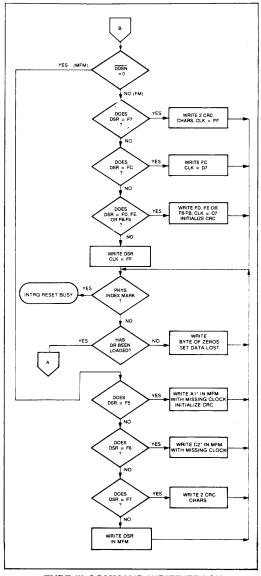

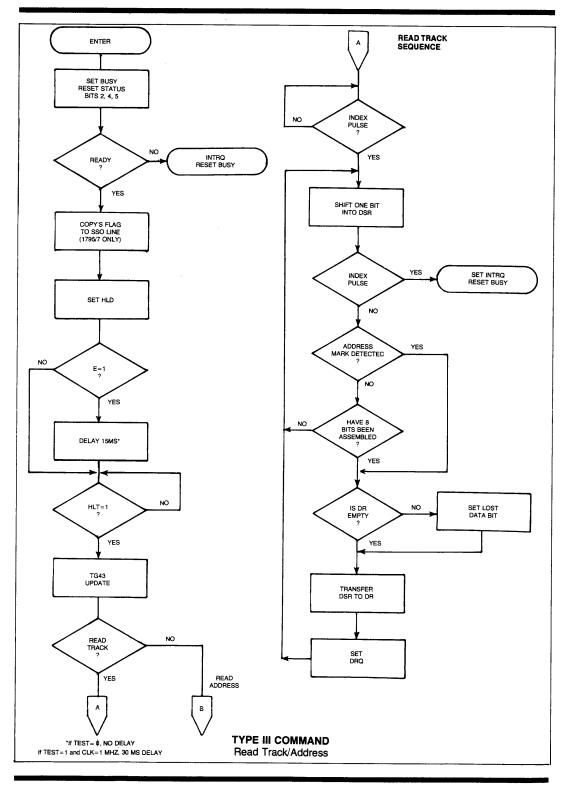

# TYPE III COMMANDS

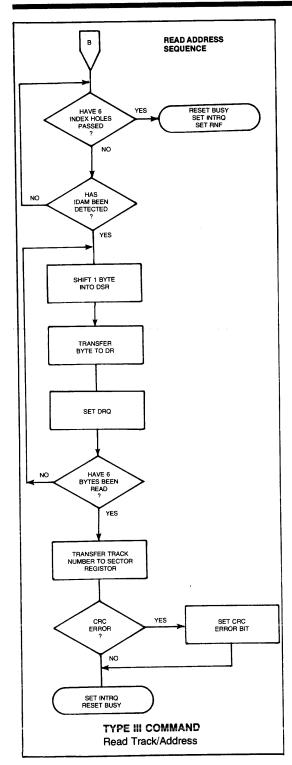

# READ ADDRESS

Upon receipt of the Read Address command, the head is loaded and the Busy Status Bit is set. The next encountered ID field is then read in from the disk, and the six data bytes of the ID field are assembled and transferred to the DR, and a DRQ is generated for each byte. The six bytes of the ID field are shown below:

| TRACK | SIDE   | SECTOR  | SECTOR | CRC | CRC |

|-------|--------|---------|--------|-----|-----|

| ADDR  | NUMBER | ADDRESS | LENGTH | 1   | 2   |

| 1     | 2      | 3       | 4      | 5   | 6   |

Although the CRC characters are transferred to the computer, the FD179X checks for validity and the CRC error status bit is set if there is a CRC error. The Track Address of the ID field is written into the sector register so that a comparison can be made by the user. At the end of the operation an interrupt is generated and the Busy Status is reset.

#### **READ TRACK**

Upon receipt of the READ track command, the head is loaded, and the Busy Status bit is set. Reading starts with the leading edge of the first encountered index pulse and continues until the next index pulse. All Gap, Header, and data bytes are assembled and transferred to the data register and DRQ's are generated for each byte. The accumulation of bytes is synchronized to each address mark encountered. An interrupt is generated at the completion of the command.

This command has several characteristics which make it suitable for diagnostic purposes. They are: the Read Gate

ENTER YES SET BUSY, RESET DRO LOST DATA, STATUS BITS 4, 5 NO INTRO RESET BUSY YES COPY S' FLAG TO SSO LINE (1795-7 ONLY) NO YES NO YES YES DR TO DSR TG43 UPDATE SET DRQ NO SET DRO DELAY 3 BYTE = 1 MHz YES

TYPE III COMMAND WRITE TRACK

is not activated during the command; no CRC checking is performed; gap information is included in the data stream; the internal side compare is not performed; and the address mark detector is on for the duration of the command. Because the A.M. detector is always on, write splices or noise may cause the chip to look for an A.M. If an address mark does not appear on schedule the Lost Data status flag is set.

The ID A.M., ID field, ID CRC bytes, DAM, Data, and Data CRC Bytes for each sector will be correct. The Gap Bytes may be read incorrectly during write-splice time because of synchronization.

TYPE III COMMAND WRITE TRACK

#### CONTROL BYTES FOR INITIALIZATION

| DATA PATTERN                               | FD179X INTERPRETATION                                                                                                                                                                                                  | FD1791/3 INTERPRETATION                                                                                                                                                               |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN DR (HEX)                                | IN FM (DDEN = 1)                                                                                                                                                                                                       | IN MFM (DDEN = 0)                                                                                                                                                                     |

| 00 thru F4 F5 F6 F7 F8 thru FB FC FD FE FF | Write 00 thru F4 with CLK = FF Not Allowed Not Allowed Generate 2 CRC bytes Write F8 thru FB, Clk = C7, Preset CRC Write FC with Clk = D7 Write FD with Clk = FF Write FE, Clk = C7, Preset CRC Write FF with Clk = FF | Write 00 thru F4, in MFM Write A1* in MFM, Preset CRC Write C2** in MFM Generate 2 CRC bytes Write F8 thru FB, in MFM Write FC in MFM Write FD in MFM Write FE in MFM Write FF in MFM |

<sup>\*</sup>Missing clock transition between bits 4 and 5

# WRITE TRACK FORMATTING THE DISK

(Refer to section on Type III commands for flow diagrams.)

Formatting the disk is a relatively simple task when operating programmed I/O or when operating under DMA with a large amount of memory. Data and gap information must be provided at the computer interface. Formatting the disk is accomplished by positioning the R/W head over the desired track number and issuing the Write Track command.

Upon receipt of the Write Track command, the head is loaded and the Busy Status bit is set. Writing starts with the leading edge of the first encountered index pulse and continues until the next index pulse, at which time the interrupt is activated. The Data Request is activated immediately upon receiving the command, but writing will not start until after the first byte has been loaded into the Data Register. If the DR has not been loaded by the time the index pulse is encountered the operation is terminated making the device Not Busy, the Lost Data Status Bit is set, and the Interrupt is activated. If a byte is not present in the DR when needed, a byte of zeroes is substituted.

This sequence continues from one index mark to the next index mark. Normally, whatever data pattern appears in the data register is written on the disk with a normal clock pattern. However, if the FD179X detects a data pattern of F5 thru FE in the data register, this is interpreted as data address marks with missing clocks or CRC generation.

The CRC generator is initialized when any data byte from F8 to FE is about to be transferred from the DR to the DSR in FM or by receipt of F5 in MFM. An F7 pattern will generate two CRC characters in FM or MFM. As a consequence, the patterns F5 thru FE must not appear in the gaps, data fields, or ID fields. Also, CRC's must be generated by an F7 pattern.

Disks may be formatted in IBM 3740 or System 34 formats with sector lengths of 128, 256, 512, or 1024 bytes.

#### TYPE IV COMMANDS

The Forced Interrupt command is generally used to terminate a multiple sector read or write command or to in-

sure Type I status in the status register. This command can be loaded into the command register at any time. If there is a current command under execution (busy status bit set) the command will be terminated and the busy status bit reset.

The lower four bits of the command determine the conditional interrupt as follows:

$I_0 = Not-Ready to Ready Transition$

11 = Ready to Not-Ready Transition

I<sub>2</sub> = Every Index Pulse

13 = Immediate Interrupt

The conditional interrupt is enabled when the corresponding bit positions of the command ( $^{1}3 \cdot ^{1}0$ ) are set to a 1. Then, when the condition for interrupt is met, the INTRQ line will go high signifying that the condition specified has occurred. If  $^{1}3 \cdot ^{1}0$  are all set to zero (HEX D0), no interrupt will occur but any command presently under execution will be immediately terminated. When using the immediately generated and the current command terminated. Reading the status or writing to the command register will not automatically clear the interrupt. The HEX D0 is the only command that will enable the immediate interrupt (HEX D8) to clear on a subsequent load command register or read status register operation. Follow a HEX D8 with D0 command.

Wait 8 micro sec (double density) or 16 micro sec (single density before issuing a new command after issuing a forced interrupt (times double when clock = 1 MHz). Loading a new command sooner than this will nullify the forced interrupt.

Forced interrupt stops any command at the end of an internal micro-instruction and generates INTRQ when the specified condition is met. Forced interrupt will wait until ALU operations in progress are complete (CRC calculations, compares, etc.).

More than one condition may be set at a time. If for example, the READY TO NOT-READY condition ( $^{1}1 = 1$ ) and the Every Index Pulse ( $^{1}2 = 1$ ) are both set, the resultant command would be HEX "DA". The "OR" function is performed so that either a READY TO NOT- READY or the next Index Pulse will cause an interrupt condition.

<sup>\*\*</sup>Missing clock transition between bits 3 & 4

# STATUS REGISTER

Upon receipt of any command, except the Force Interrupt command, the Busy Status bit is set and the rest of the status bits are updated or cleared for the new command. If the Force Interrupt Command is received when there is a current command under execution, the Busy status bit is reset, and the rest of the status bits are unchanged. If the Force Interrupt command is received when there is not a current command under execution, the Busy Status bit is reset and the rest of the status bits are updated or cleared. In this case, Status reflects the Type I commands.

The user has the option of reading the status register through program control or using the DRQ line with DMA or interrupt methods. When the Data register is read the DRQ bit in the status register and the DRQ line are automatically reset. A write to the Data register also causes both DRQ's to reset.

The busy bit in the status may be monitored with a user program to determine when a command is complete, in lieu of using the INTRQ line. When using the INTRQ, a busy status check is not recommended because a read of the status register to determine the condition of busy will reset the INTRQ line.

The format of the Status Register is shown below:

| (BITS)          |    |            |    |   |    |    |    |

|-----------------|----|------------|----|---|----|----|----|

| 7 6 5 4 3 2 1 0 |    |            |    |   |    |    | 0  |

| S7              | S6 | <b>S</b> 5 | S4 | S | S2 | S1 | S0 |

Status varies according to the type of command executed as shown in Table 4.

Because of internal sync cycles, certain time delays must be observed when operating under programmed I/O. They are: (times double when clock = 1 MHz)

|                          |                                 | Delay Reg'd. |       |  |

|--------------------------|---------------------------------|--------------|-------|--|

| Operation                | Next Operation                  | FM           | MFM   |  |

| Write to<br>Command Reg. | Read Busy Bit<br>(Status Bit 0) | 12 µS        | 6 μs  |  |

| Write to<br>Command Reg. | Read Status<br>Bits 1-7         | 28 µs        | 14 μs |  |

| Write Any<br>Register    | Read From Diff.<br>Register     | 0            | 0     |  |

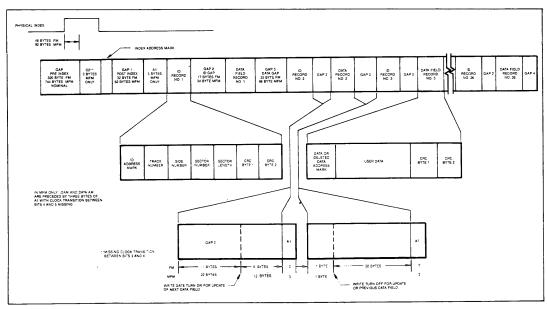

# IBM 3740 FORMAT - 128 BYTES/SECTOR

Shown below is the IBM single-density format with 128 bytes/sector. In order to format a diskette, the user must issue the Write Track command, and load the data register with the following values. For every byte to be written, there is one Data Request.

# IBM 3740 FORMAT - 128 BYTES/SECTOR

Shown below is the IBM single-density format with 128 bytes/sector. In order to format a diskette, the user must issue the Write Track command, and load the data register with the following values. For every byte to be written, there is one Data Request.

| NUMBER<br>OF BYTES | HEX VALUE OF<br>BYTE WRITTEN |

|--------------------|------------------------------|

| 40                 | FF (or 00)1                  |

| 6                  | 00                           |

| 1                  | FC (Index Mark)              |

| * 26               | FF (or 00) <sup>1</sup>      |

| 6                  | 00                           |

| 1                  | FE (ID Address Mark)         |

| 1                  | Track Number                 |

| 1                  | Side Number (00 or 01)       |

| 1                  | Sector Number (1 thru 1A)    |

| 1 1                | 00 (Sector Length)           |

| 1                  | F7 (2 CRC's written)         |

| 11                 | FF (or 00) <sup>1</sup>      |

| 6                  | 00                           |

| 1                  | FB (Data Address Mark)       |

| 128                | Data (IBM uses E5)           |

| 1                  | F7 (2 CRC's written)         |

| 27                 | FF (or 00) <sup>1</sup>      |

| 247**              | FF (or 00) <sup>1</sup>      |

<sup>\*</sup>Write bracketed field 26 times

## IBM SYSTEM 34 FORMAT- 256 BYTES/SECTOR

Shown below is the IBM dual-density format with 256 bytes/sector. In order to format a diskette the user must issue the Write Track command and load the data register with the following values. For every byte to be written, there is one data request.

| NUMBER<br>OF BYTES | HEX VALUE OF<br>BYTE WRITTEN |  |  |  |

|--------------------|------------------------------|--|--|--|

| 80                 | 4E                           |  |  |  |

| 12                 | 00                           |  |  |  |

| 3                  | F6 (Writes C2)               |  |  |  |

| 1                  | FC (Index Mark)              |  |  |  |

| * 50               | 4E                           |  |  |  |

| 12                 | 00                           |  |  |  |

| 3                  | F5 (Writes A1)               |  |  |  |

| 1                  | FE (ID Address Mark)         |  |  |  |

| 1                  | Track Number (0 thru 4C)     |  |  |  |

| 1                  | Side Number (0 or 1)         |  |  |  |

| 1                  | Sector Number (1 thru 1A)    |  |  |  |

| 1                  | 01 (Sector Length)           |  |  |  |

| 1                  | F7 (2 CRCs written)          |  |  |  |

| 22                 | 4E                           |  |  |  |

| 12                 | 00                           |  |  |  |

| 3                  | F5 (Writes A1)               |  |  |  |

| 1                  | FB (Data Address Mark)       |  |  |  |

| 256                | DATA                         |  |  |  |

| 1                  | F7 (2 CRCs written)          |  |  |  |

| 54                 | 4E                           |  |  |  |

| 598**              | 4E                           |  |  |  |

<sup>\*</sup>Write bracketed field 26 times

<sup>\*\*</sup>Continue writing until FD179X interrupts out. Approx. 598 bytes.

**IBM TRACK FORMAT**

<sup>\*\*</sup>Continue writing until FD179X interrupts out. Approx. 247 bytes.

<sup>1-</sup>Optional '00' on 1795/7 only.

#### 1. NON-IBM FORMATS

Variations in the IBM formats are possible to a limited extent if the following requirements are met:

- 1) Sector size must be 128, 256, 512 or 1024 bytes.

- 2) Gap 2 cannot be varied from the IBM format.

- 3) 3 bytes of A1 must be used in MFM.

In addition, the Index Address Mark is not required for operation by the FD179X. Gap 1, 3, and 4 lengths can be as short as 2 bytes for FD179X operation, however PLL lock up time, motor speed variation, write-splice area, etc. will add more bytes to each gap to achieve proper operation. It is recommended that the IBM format be used for highest system reliability.

|           | FM                        | MFM                                     |

|-----------|---------------------------|-----------------------------------------|

| Gap I     | 16 bytes FF               | 32 bytes 4E                             |

| Gap II    | 11 bytes FF               | 22 bytes 4E                             |

| *         | 6 bytes 00                | 12 bytes 00<br>3 bytes A1               |

| Gap III** | 10 bytes FF<br>4 bytes 00 | 24 bytes 4E<br>8 bytes 00<br>3 bytes A1 |

| Gap IV    | 16 bytes FF               | 16 bytes 4E                             |

<sup>\*</sup>Byte counts must be exact.

<sup>\*\*</sup>Byte counts are minimum, except exactly 3 bytes of A1 must be written.

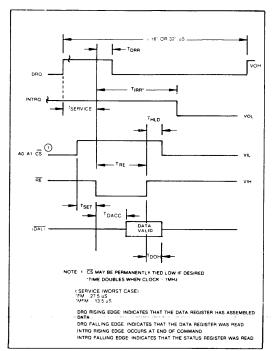

**READ ENABLE TIMING**

# **TIMING CHARACTERISTICS**

$T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ ,  $V_{DD} = + 12\text{V} \pm .6\text{V}$ ,  $V_{SS} = 0\text{V}$ ,  $V_{CC} = +5\text{V} \pm .25\text{V}$

# READ ENABLE TIMING (See Note 6, Page 21)

| SYMBOL | CHARACTERISTIC         | MIN. | TYP. | MAX. | UNITS | CONDITIONS    |

|--------|------------------------|------|------|------|-------|---------------|

| TSET   | Setup ADDR & CS to RE  | 50   |      |      | nsec  |               |

| THLD   | Hold ADDR & CS from RE | 10   |      |      | nsec  |               |

| TRE    | RE Pulse Width         | 400  |      |      | nsec  | $C_L = 50 pf$ |

| TDRR   | DRQ Reset from RE      |      | 400  | 500  | nsec  | ,             |

| TIRR   | INTRQ Reset from RE    |      | 500  | 3000 | nsec  | See Note 5    |

| TDACC  | Data Access from RE    |      |      | 350  | nsec  | $C_L = 50 pf$ |

| TDOH   | Data Hold From RE      | 50   |      | 150  | nsec  | C∟ = 50 pf    |

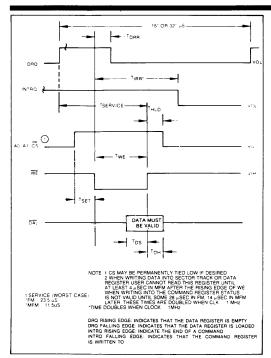

# WRITE ENABLE TIMING (See Note 6, Page 21)

| SYMBOL | CHARACTERISTIC         | MIN. | TYP. | MAX. | UNITS | CONDITIONS |

|--------|------------------------|------|------|------|-------|------------|

| TSET   | Setup ADDR & CS to WE  | 50   |      |      | nsec  |            |

| THLD   | Hold ADDR & CS from WE | 10   |      |      | nsec  |            |

| TWE    | WE Pulse Width         | 350  |      |      | nsec  |            |

| TDRR   | DRQ Reset from WE      |      | 400  | 500  | nsec  |            |

| TIRR   | INTRQ Reset from WE    |      | 500  | 3000 | nsec  | See Note 5 |

| TDS    | Data Setup to WE       | 250  |      |      | nsec  |            |

| TDH    | Data Hold from WE      | 70   |      |      | nsec  |            |

|        | 1                      |      | 1    |      |       |            |

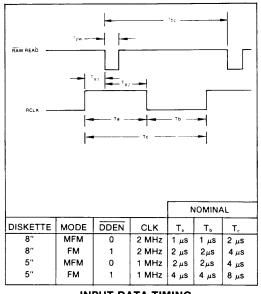

# INPUT DATA TIMING

# WRITE ENABLE TIMING

# INPUT DATA TIMING:

| NFOT DATA TIMING. |                       |      |      |      |       |                |  |

|-------------------|-----------------------|------|------|------|-------|----------------|--|

| SYMBOL            | CHARACTERISTIC        | MIN. | TYP. | MAX. | UNITS | CONDITIONS     |  |

| Tpw               | Raw Read Pulse Width  | 100  | 200  |      | nsec  | See Note 1     |  |

| tbc               | Raw Read Cycle Time   | 1500 | 2000 |      | nsec  | 1800 ns @ 70°C |  |

| Тс                | RCLK Cycle Time       | 1500 | 2000 |      | nsec  | 1800 ns @ 70°C |  |

| Tx <sub>1</sub>   | RCLK hold to Raw Read | 40   |      |      | nsec  | See Note 1     |  |

| Tx2               | Raw Read hold to RCLK | 40   |      |      | nsec  | See Note 1     |  |

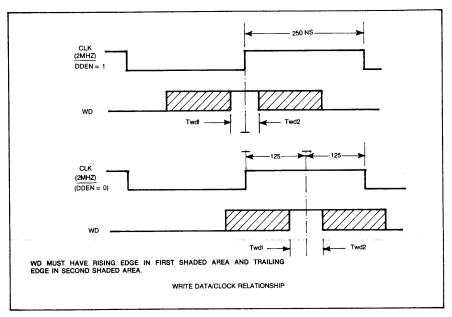

# WRITE DATA TIMING: (ALL TIMES DOUBLE WHEN CLK = 1 MHz) (See Note 6, Page 21)

| SYMBOL | CHARACTERISTICS                 | MIN.      | TYP.       | MAX.       | UNITS        | CONDITIONS             |

|--------|---------------------------------|-----------|------------|------------|--------------|------------------------|

| Twp    | Write Data Pulse Width          |           | 500<br>200 | 650<br>350 | nsec<br>nsec | FM<br>MFM              |

| Twg    | Write Gate to Write Data        |           | 2 1        | 350        | μsec<br>μsec | FM<br>MFM              |

| Tbc    | Write data cycle Time           | 1         | 2,3, or 4  |            | μsec         | ±CLK Error             |

| Ts     | Early (Late) to Write Data      | 125       | , ,        |            | nsec         | MFM                    |

| Th     | Early (Late) From<br>Write Data | 125       |            |            | nsec         | MFM                    |

| Twf    | Write Gate off from WD          |           | 2<br>1     |            | μsec<br>μsec | FM<br>MFM              |

| Twdl   | WD Valid to Clk                 | 100<br>50 |            |            | nsec<br>nsec | CLK=1 MHZ<br>CLK=2 MHZ |

| Twd2   | WD Valid after CLK              | 100<br>30 |            |            | nsec<br>nsec | CLK=1 MHZ<br>CLK=2 MHZ |

WRITE DATA TIMING

# MISCELLANEOUS TIMING: (Times Double When Clock = 1 MHz) (See Note 6, Page 21)